Confronto tra wafer SOI e wafer di silicio: Cosa è meglio per il vostro progetto di semiconduttori?

1 Introduzione

Il SOI è un materiale semiconduttore con una struttura a strati di silicio, strato isolante e substrato di silicio. Rispetto ai wafer di silicio, comunemente utilizzati nei dispositivi a semiconduttore, esistono differenze significative tra i due in termini di struttura del materiale, caratteristiche delle prestazioni, aree di applicazione, ecc.

La struttura SOI migliora le prestazioni e l'affidabilità del dispositivo grazie alla struttura stratificata strato di silicio-strato isolante-substrato di silicio, ma il costo di produzione è più elevato. I wafer di silicio tradizionali, invece, hanno costi di produzione inferiori e sono adatti a un'ampia gamma di produzioni di circuiti integrati.

![]()

2 Che cos'è il SOI?

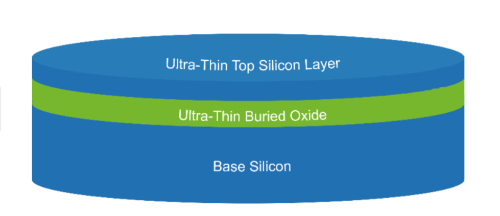

SOI è l'acronimo di Silicon-On-Insulator. In SOI, la superficie di un chip di silicio è ricoperta da un materiale isolante (solitamente biossido di silicio), sul quale viene poi fatto crescere uno strato di silicio. Questa struttura crea una struttura a strati strato di silicio-strato isolante-substrato di silicio.

2.1 La struttura del SOI

La struttura di un SOI (Silicon-On-Insulator) è composta dalle seguenti parti principali:

- Strato di Si: In cima alla struttura SOI si trova uno strato di cristalli di silicio (Si) che di solito hanno le proprietà elettroniche e le caratteristiche del dispositivo desiderate. Questo strato può essere preparato con le tecniche standard di crescita dei wafer di silicio.

- Strato isolante: Al di sotto dello strato di Si si trova un materiale isolante, solitamente biossido di silicio (SiO2). Lo scopo dello strato isolante è quello di isolare lo strato di silicio superiore dal substrato di silicio sottostante, riducendo così la diafonia tra i transistor.

- Substrato di silicio: Il substrato di silicio è la parte inferiore della struttura SOI e di solito è il substrato di supporto principale del wafer. Il substrato di silicio è solitamente silicio cristallino, che fornisce supporto meccanico e stabilità alla struttura SOI.

2.2 Classificazione dei SOI

Esistono diverse varianti della tecnologia SOI. I SOI possono essere classificati secondo diversi criteri, a seconda della loro struttura e del loro scopo.

2.2.1 Classificazione per tipo di struttura

SOI comune (c-SOI): Utilizza il comune metodo di fabbricazione SOI che consiste nel depositare uno strato isolante (di solito biossido di silicio) sulla superficie di un wafer di silicio, per poi far crescere uno strato di silicio sopra di esso. In un comune SOI, lo spessore dello strato di silicio è solitamente paragonabile allo spessore dello strato isolante, formando una struttura strato di silicio-strato isolante-substrato di silicio.

SOI parziale (p-SOI): Il SOI parziale si differenzia dal SOI normale in quanto lo spessore dello strato di silicio è più sottile, solo una frazione dello spessore dello strato isolante. In un SOI parziale, lo spessore dello strato di silicio è tipicamente inferiore allo spessore dello strato isolante, dando alla struttura SOI parziale uno strato di silicio più sottile.

SOI inverso (r-SOI): Il SOI inverso è una struttura SOI speciale, diversa dal SOI normale e dal SOI parziale. Nel SOI inverso, lo strato di silicio viene rimosso dal substrato e riattaccato allo strato isolante. Questa struttura consente al transistor di trovarsi sopra lo strato isolante e al substrato di silicio di trovarsi sotto lo strato isolante, cambiando così la topologia della struttura SOI convenzionale.

Queste diverse varianti di SOI offrono diversi vantaggi e possibilità di applicazione in applicazioni specifiche. I SOI comuni sono comunemente utilizzati in applicazioni ad alte prestazioni e a bassa potenza, mentre i SOI parziali sono più adatti per la fabbricazione di alcuni dispositivi a radiofrequenza (RF) e i SOI invertiti offrono ulteriori vantaggi in applicazioni specifiche, come i dispositivi ad alta velocità e a bassa perdita.

2.2.2 Classificazione per tipo di substrato cristallino

Silicio su isolatore (SIMOX-SOI): SIMOX (Separation by IMplantation of OXygen) è un metodo comune di preparazione del SOI, noto anche come silicio su isolante. Nella preparazione SIMOX-SOI, gli ioni di ossigeno vengono iniettati nel wafer e poi trattati termicamente per far sì che gli ioni di ossigeno formino uno strato isolante di ossido di silicio nel wafer, dando luogo alla formazione della struttura SOI.

Ultra-Thin SOI (UTSOI): L'Ultra-Thin SOI è un tipo speciale di struttura SOI caratterizzata da uno strato di silicio molto sottile, tipicamente compreso tra pochi nanometri e decine di nanometri. Il metodo di preparazione di UTSOI prevede solitamente speciali tecniche di crescita o stripping per formare uno strato di silicio molto sottile su un substrato di silicio per realizzare la struttura SOI.

SOI epitassiale (Epi-SOI): L'Epi-SOI è un metodo per formare strutture SOI facendo crescere uno strato di silicio epitassiale su un substrato di silicio. In Epi-SOI, lo strato di silicio epitassiale viene fatto crescere su un substrato di silicio e ha tipicamente la stessa struttura cristallina del substrato, ma con uno strato isolante tra lo strato di silicio e il substrato.

Il SIMOX-SOI è comunemente usato per la fabbricazione di circuiti integrati, l'UTSOI è comunemente usato per applicazioni ad alte prestazioni e basso consumo come le comunicazioni mobili e i dispositivi RF, mentre l'Epi-SOI fornisce una migliore qualità del cristallo e un migliore controllo strutturale per le esigenze specifiche di fabbricazione dei dispositivi.

2.2.3 Classificazione in base allo spessore dello strato di silicio

Thin-Film SOI: nel Thin-Film SOI, lo spessore dello strato di silicio è solitamente compreso tra decine di nanometri e centinaia di nanometri. Questo tipo di struttura SOI è spesso utilizzato per fabbricare dispositivi ultrasottili, come dispositivi elettronici a bassa potenza, dispositivi optoelettronici e così via. I SOI a strato sottile sono tipicamente preparati utilizzando una serie di fasi di lavorazione di precisione, tra cui tecniche come la lucidatura meccanica chimica (CMP) e l'iniezione e lo stripping di ioni di idrogeno.

SOI a film spesso: nei SOI a film spesso, lo spessore dello strato di silicio è in genere di diverse centinaia di nanometri o più. Questo tipo di struttura SOI è tipicamente utilizzato per fabbricare dispositivi tradizionali a circuito integrato, come microprocessori, memorie, ecc. I SOI a strato spesso vengono solitamente preparati con diverse tecniche come SIMOX, Unibond e Smart Cut. Queste tecniche consentono di preparare strati di silicio con spessori elevati per soddisfare le esigenze della produzione di circuiti integrati convenzionali.

2.2.4 Classificazione in base al metodo di controllo della carica per i transistor

SOI completamente impoverito (FD-SOI): In FD-SOI, l'intero strato di silicio è in uno stato esaurito, il che significa che la carica del transistor è completamente controllata dal gate sovrastante e non è influenzata dal substrato inferiore. Controllando con precisione lo spessore dello strato di silicio e le caratteristiche dello strato isolante, è possibile ottenere un intero strato di silicio allo stato esaurito. Questa struttura offre un migliore controllo della carica e una minore corrente di dispersione. Il SOI completamente impoverito è spesso considerato come una tecnologia di semiconduttori di prossima generazione, con prestazioni più elevate e consumi più bassi, e sta quindi ricevendo sempre più attenzione nella progettazione e nella fabbricazione dei chip.

SOI parzialmente impoverito (pFD-SOI): Nel SOI parzialmente impoverito, una parte dello strato di silicio si trova in uno stato impoverito mentre un'altra parte rimane in uno stato non impoverito. In genere, con una progettazione e un processo adeguati, è possibile realizzare che solo una parte dello strato di silicio (di solito la parte superiore) sia in uno stato di esaurimento. Il SOI parzialmente impoverito può essere utilizzato in applicazioni ad alte prestazioni e basso consumo, come le comunicazioni mobili, i dispositivi a radiofrequenza (RF) e altri settori. Offre opportunità per un migliore controllo della carica e per l'ottimizzazione delle prestazioni.

La tabella seguente illustra le varie strutture SOI, le loro caratteristiche e le loro applicazioni tipiche, fornendo una panoramica completa delle differenze tra ciascun tipo di SOI.

Stanford Advanced Materials (SAM) e altri fornitori affidabili offrono wafer SOI di varie dimensioni e tipologie. Queste scelte sono personalizzate per soddisfare le vostre specifiche.

Tabella 1 Confronto tra i diversi tipi di wafer SOI

|

Classificazione |

Tipo |

Breve descrizione e applicazioni |

|

Tipo di struttura |

c-SOI |

Spessore dello strato di silicio simile allo strato isolante. Utilizzato in applicazioni ad alte prestazioni e basso consumo. |

|

p-SOI |

Strato di silicio più sottile rispetto allo strato isolante. Adatto per la fabbricazione di dispositivi RF specifici. |

|

|

r-SOI |

Strato di silicio riattaccato sopra lo strato isolante, invertendo la struttura. Per dispositivi ad alta velocità e a bassa perdita. |

|

|

Tipo di substrato di cristallo |

SIMOX-SOI |

Gli ioni di ossigeno formano lo strato isolante di ossido di silicio. Comune nella produzione di circuiti integrati. |

|

UTSOI |

Strato di silicio ultrasottile per applicazioni ad alte prestazioni e basso consumo, come dispositivi mobili e RF. |

|

|

Epi-SOI |

Strato epitassiale cresciuto su un substrato di silicio per dispositivi che richiedono una migliore qualità del cristallo. |

|

|

Spessore dello strato di silicio |

SOI a film sottile |

Strato di silicio spesso da decine a centinaia di nanometri. Per dispositivi elettronici e optoelettronici a bassa potenza. |

|

SOI a film spesso |

Strato di silicio spesso diverse centinaia di nanometri. Utilizzato nei dispositivi IC tradizionali come i microprocessori. |

|

|

Metodo di controllo della carica per i transistor |

FD-SOI |

L'intero strato di silicio è stato privato della carica per un controllo completo. Punta a tecnologie di nuova generazione ad alte prestazioni e basso consumo. |

|

pFD-SOI |

Impoverimento parziale dello strato di silicio. Applicato in applicazioni ad alte prestazioni e basso consumo (ad esempio, cellulari, RF). |

3 SOI e wafer di silicio: quali sono i migliori?

La tecnologia SOI (Silicon-on-Insulator) e i wafer di silicio tradizionali sono stati a lungo determinanti nel panorama della produzione di semiconduttori, ciascuno dei quali possiede caratteristiche strutturali e capacità prestazionali distinte. Con l'aumento della domanda di dispositivi elettronici più efficienti, più veloci e più piccoli, la comprensione delle differenze tra questi due materiali fondamentali diventa cruciale. Questo confronto cerca di evidenziare le sfumature strutturali e le prestazioni dei wafer di SOI e di silicio.

3.1 Le differenze strutturali tra wafer di silicio e SOI

Wafer di silicio: Un wafer di silicio tradizionale è costituito da un singolo cristallo di silicio e da una struttura di silicio monocristallino. In un wafer di silicio tradizionale, la superficie del wafer è solitamente costituita da un singolo cristallo di silicio senza alcuno strato isolante aggiuntivo. I wafer di silicio hanno una struttura semplice e sono il substrato più comune per i dispositivi a semiconduttore.

SOI: nella struttura SOI, la superficie del wafer di silicio è ricoperta da uno strato di materiale isolante (solitamente biossido di silicio). Questo strato di materiale isolante viene comunemente utilizzato per isolare lo strato di silicio dal substrato di silicio, riducendo così la diafonia tra i dispositivi e migliorandone le prestazioni e l'affidabilità. Sopra lo strato isolante, viene fatto crescere un altro strato di silicio per formare una struttura a strati: strato di silicio-strato isolante-substrato di silicio. Lo strato di silicio è lo strato attivo del transistor e di solito ha le proprietà elettroniche desiderate e le prestazioni del dispositivo. Lo spessore dello strato isolante può essere regolato in base ai requisiti dell'applicazione per controllare le caratteristiche e le prestazioni del dispositivo.

I SOI presentano uno strato isolante aggiuntivo rispetto ai wafer di silicio convenzionali. La presenza di questo strato isolante migliora le prestazioni e l'affidabilità del dispositivo, ma aumenta anche la complessità e il costo di fabbricazione.

3.2 Le differenze di prestazioni tra i wafer SOI e quelli in silicio

- Soppressione della diafonia: Ogni transistor nella struttura SOI è isolato da uno strato isolante, riducendo in modo significativo gli effetti di diafonia tra i dispositivi. La presenza dello strato isolante riduce l'effetto di accoppiamento elettromagnetico tra i transistor, migliorando le prestazioni e l'affidabilità del dispositivo. La diafonia è solitamente un problema serio nei circuiti integrati ad alta densità e l'uso dei SOI riduce efficacemente l'effetto della diafonia sulle prestazioni del dispositivo.

- Vantaggi in termini di velocità e potenza: I dispositivi SOI hanno in genere una velocità superiore e un'efficienza energetica inferiore. Grazie alla ridotta resistenza al movimento delle cariche nella struttura SOI, gli elettroni nello strato di silicio possono muoversi più velocemente, con conseguente aumento della velocità di commutazione e riduzione del consumo energetico. Ciò conferisce al SOI un chiaro vantaggio nelle applicazioni ad alte prestazioni e basso consumo, come le comunicazioni mobili e l'informatica ad alte prestazioni.

- Maggiore resistenza alle radiazioni: La struttura SOI migliora la resistenza alle radiazioni del dispositivo, rendendolo più adatto ad applicazioni in ambienti con radiazioni elevate. Grazie alla presenza di uno strato isolante, i dispositivi SOI sono meno sensibili alle radiazioni e trovano quindi un'ampia gamma di applicazioni nello spazio, nelle centrali nucleari e in altri dispositivi elettronici in ambienti ad alte radiazioni. La maggiore resistenza alle radiazioni è fondamentale per alcune applicazioni specifiche come quelle aerospaziali e nucleari.

3.3 Come vengono utilizzati i wafer SOI e di silicio

--Aree di applicazione del SOI

Applicazioni ad alte prestazioni: Il SOI è spesso utilizzato in applicazioni che richiedono prestazioni elevate, come i chip per computer ad alta velocità e i processori grafici. Le sue caratteristiche di bassa impedenza di movimento della carica e di soppressione della diafonia lo rendono ideale per realizzare prestazioni elevate.

Applicazioni a basso consumo: Poiché i dispositivi SOI hanno un consumo energetico ridotto e velocità di commutazione più elevate, hanno un'ampia gamma di applicazioni in settori come i dispositivi mobili e le reti di sensori wireless che richiedono un basso consumo energetico. Ad esempio, i chip di dispositivi come smartphone e tablet PC utilizzano spesso la tecnologia SOI.

Applicazioni a radiofrequenza (RF): Le caratteristiche di alta velocità e bassa perdita del SOI gli conferiscono un enorme vantaggio nelle applicazioni a radiofrequenza (RF). Ad esempio, i dispositivi SOI possono essere utilizzati per fabbricare moduli front-end RF ad alte prestazioni, commutatori d'antenna, amplificatori di potenza e altro ancora.

Applicazioni in ambienti ad alta radiazione: La struttura SOI migliora la resistenza alle radiazioni del dispositivo, rendendolo importante per le applicazioni nello spazio, nelle centrali nucleari e in altri ambienti ad alta radiazione. Ad esempio, le sonde spaziali, i sistemi di comunicazione satellitare e altri dispositivi che devono funzionare in un ambiente ad alte radiazioni utilizzano spesso la tecnologia SOI.

--Applicazioni dei wafer di silicio tradizionali

I wafer di silicio tradizionali sono ampiamente utilizzati nella produzione di vari circuiti integrati, tra cui microprocessori, memorie, sensori e così via. I wafer di silicio sono la base per la produzione di circuiti integrati (IC). Vari tipi di circuiti integrati, tra cui microprocessori, memorie, circuiti analogici, circuiti digitali e così via, sono prodotti stratificando diversi materiali e circuiti su wafer di silicio. Quasi tutti i dispositivi elettronici utilizzano chip tradizionali per la produzione di wafer di silicio, come i personal computer, gli elettrodomestici e i sistemi elettronici automobilistici. Può anche essere utilizzato per produrre una varietà di dispositivi elettronici comunemente usati in campo industriale, celle solari e dispositivi biomedici. Grazie alle eccellenti proprietà dei semiconduttori, ai processi di produzione maturi e al controllo di qualità stabile, i wafer di silicio sono ampiamente utilizzati nei processi di produzione e di ricerca, e anche la soglia tecnologica è più bassa rispetto al SOI.

3.4 Come vengono prodotti i wafer di SOI e di silicio

--Metodi di preparazione dei cristalli SOI

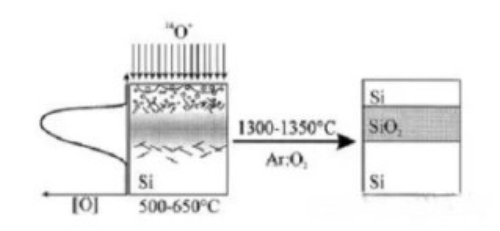

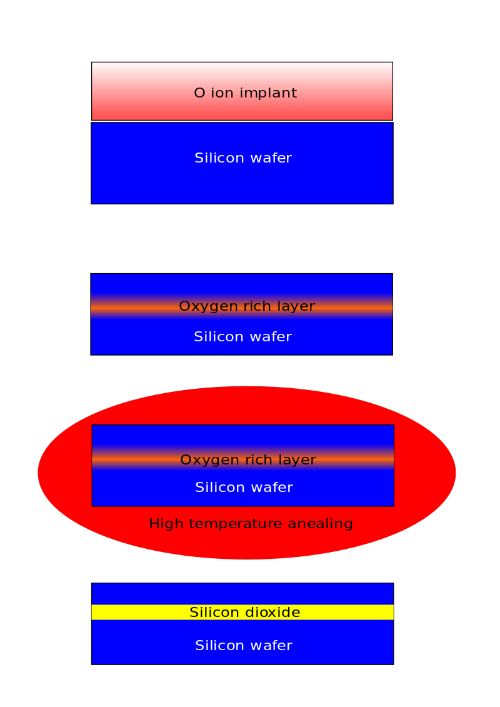

3.4.1 Tecnologia SIMOX

Latecnologia SIMOX, acronimo di Separation by IMplantation of OXygen, è uno dei metodi pionieristici per la preparazione dei wafer SOI (Silicon-On-Insulator). Questa tecnica sfrutta l'impianto di ioni per introdurre ioni di ossigeno nel silicio, formando uno strato di isolamento di ossido sepolto. Questo strato di ossido sepolto isola efficacemente il substrato dallo strato superiore di film sottile di silicio. Il processo prevede l'iniezione di ioni di ossigeno nel wafer di silicio al di sotto della superficie, in genere con un livello di energia di 200 keV e una dose di 1,8 × 10^18 cm^-2. Successivamente, un processo di ricottura ad alta temperatura della durata di 3-6 ore a 1350°C facilita le reazioni chimiche tra gli ioni di ossigeno e gli atomi di silicio all'interno del wafer, portando alla formazione di uno strato isolante di biossido di silicio con uno spessore inferiore a 240 nm sotto la superficie. Al di sopra di questo strato isolante si forma uno strato di silicio cristallino, che dà origine alla struttura SOI composta da film sottile di silicio - strato isolante di biossido di silicio - substrato di silicio.

I vantaggi della tecnologia SIMOX includono la formazione di uno strato di ossido sepolto (BOX) relativamente uniforme. Lo spessore dello strato di silicio in cima al BOX può essere controllato con precisione gestendo l'energia di iniezione. Inoltre, l'interfaccia tra il BOX e lo strato di silicio superiore rimane notevolmente piatta.

Tuttavia, la tecnologia SIMOX ha i suoi limiti. L'intervallo di regolazione dello spessore del BOX e dello strato di silicio superiore è relativamente limitato. In genere, lo spessore del BOX non supera i 240 nm, poiché strati troppo sottili possono provocare una rottura tra lo strato superiore e il substrato, accompagnata da un aumento della capacità parassita. Analogamente, lo spessore del film di silicio superiore è solitamente limitato a 300 nm, rendendo necessaria una costosa crescita epitassiale del silicio e un successivo trattamento di appiattimento con lucidatura meccanica chimica (CMP). Inoltre, SIMOX può indurre danni al film superficiale e la qualità del cristallo del film di silicio superiore può non corrispondere a quella del silicio monocristallino sfuso. Inoltre, la qualità cristallina del SiO2 interrato è inferiore a quella ottenuta con l'ossidazione termica. L'implementazione di SIMOX richiede attrezzature specializzate per l'impianto di ioni, come costose macchine per l'iniezione di ossigeno a grande flusso, oltre a prolungati processi di ricottura ad alta temperatura, che contribuiscono ad aumentare i costi di produzione.

3.4.2 Tecnologia BESOI

Latecnologia BESOI (Bond and Etch Back Silicon-On-Insulator) prevede l'incollaggio ravvicinato di due wafer, creando uno strato di biossido di silicio come strato di ossido sepolto tra di essi. Successivamente, la tecnologia di retroincisione viene impiegata per regolare con precisione lo spessore di un wafer per ottenere lo spessore desiderato per i wafer SOI.

Il processo BESOI inizia trattando un wafer (wafer A) con l'ossidazione termica, creando uno strato di ossido, mentre l'altro wafer (wafer B) viene sottoposto a incollaggio a bassa temperatura con la superficie ossidata del wafer A. Questo processo di incollaggio, noto come Silicon Fusion Bonding (SFB), prevede diverse fasi:

Trattamento idrofilo: Entrambi i wafer sono sottoposti a un trattamento idrofilo a bassa temperatura (400°C) per indurre la formazione di legami idrossilici (OH) sulle loro superfici.

Legame attraverso la forza di Van der Waals: I due wafer vengono quindi messi a contatto e i legami OH facilitano il loro legame attraverso la forza di Van der Waals.

Ricottura termica: La ricottura termica ad alta temperatura (1100°C) viene condotta per allontanare gli ioni idrogeno, favorendo la formazione di legami Si-O-Si all'interfaccia, rafforzando così il legame.

Back-etching: l' eccesso di silicio di un wafer viene rimosso con la tecnologia del back-engraving, lasciando lo spessore desiderato per il film sottile di silicio superiore. La successiva ricottura e la lucidatura meccanica chimica (CMP) assicurano la formazione di una superficie liscia e pulita per i wafer SOI.

La tecnologia BESOI offre diversi vantaggi rispetto alla tecnologia SIMOX. Ad esempio, evita i problemi legati ai danni da iniezione e garantisce la formazione di uno strato di ossido sepolto ossidato termicamente con una minore densità di difetti e fori di spillo. Inoltre, il film di silicio superiore prodotto con BESOI è costituito da silicio monocristallino di alta qualità, che migliora le prestazioni complessive del dispositivo.

Tuttavia, la tecnologia BESOI presenta anche delle sfide. È difficile ottenere film di silicio superiore molto sottili e il controllo dei difetti di interfaccia e dell'omogeneità del film di silicio superiore rimane una sfida. Inoltre, il processo prevede fasi di retroincisione e CMP ad alto costo, che comportano un notevole spreco di materiale per i wafer, che non può essere riciclato e contribuisce ad aumentare i costi di produzione.

3.4.3 Tecnologia Smart-Cut

La tecnologia Smart-Cut deriva dalla BESOI: si preparano prima due wafer di silicio; uno dei wafer viene ossidato termicamente per formare uno strato di SiO2, quindi si iniettano ioni di idrogeno nel substrato del wafer; l'altro wafer non deve essere lavorato; analogamente a BESOI, i due wafer vengono incollati insieme; dopo l'incollaggio, i wafer iniettati di ioni di idrogeno si rompono all'interfaccia arricchita di ioni di idrogeno mediante una reazione termica a 400-600 °C; infine, l'interfaccia tra la superficie rotta e lo strato di ossido forma uno strato di film di silicio dopo un trattamento ad alta temperatura (1100 °C) per allontanare gli ioni di idrogeno. Dopo l'incollaggio, i wafer iniettati con ioni di idrogeno si fratturano nel punto di arricchimento degli ioni di idrogeno e si forma uno strato di film sottile di silicio tra la superficie di frattura e lo strato di ossido; infine, dopo il trattamento ad alta temperatura (1100 ° C), gli ioni di idrogeno si trasformano in uno strato di film sottile di silicio.C), gli ioni di idrogeno vengono allontanati, in modo che l'interfaccia incollata formi un legame Si-O-Si, che rafforzerà il legame chimico e migliorerà la qualità dello strato di film sottile di silicio, quindi la superficie verrà appiattita mediante trattamento CMP.

Smart-Cut è simile a BESOI in quanto il film di silicio superiore è silicio sfuso e il BOX è un film ossidato termicamente. Lo spessore dello strato BOX e del film di silicio superiore può essere regolato in un ampio intervallo e lo spessore del film di silicio superiore è controllato utilizzando l'energia dell'impianto ionico, in modo da ottenere un film di silicio superiore con uno spessore molto sottile e una buona uniformità. Inoltre, il materiale del wafer spogliato può essere riutilizzato, consentendo così una riduzione dei costi.

--Metodo di preparazione dei cristalli di silicio

Il metodo Czochralski è ampiamente utilizzato per la crescita dei cristalli di silicio, sfruttando un crogiolo pieno di silicio riscaldato per mantenere una temperatura di 1685°C. Questa temperatura supera il punto di fusione. Questa temperatura supera il punto di fusione del silicio di circa 100°C, rendendo il silicio nel crogiolo fuso. Nella parte superiore del crogiolo si trova un'asta di sollevamento, dotata di un dispositivo meccanico che le consente di sollevarsi e ruotare liberamente. Un piccolo pezzo di silicio monocristallino, che funziona da "seme", è fissato in cima alla leva. Questo cristallo seme avvia l'attrazione degli atomi di silicio circostanti, organizzandoli in una struttura cristallina. Mentre il cristallo sale e ruota gradualmente, le sezioni estratte rimangono parte dello stesso cristallo singolo. Il grande cristallo singolo risultante misura fino a 200 millimetri di diametro, più spesso di un braccio medio. Questo cristallo non presenta interfacce o difetti, incarnando la massima perfezione raggiungibile nei cristalli singoli prodotti dall'uomo.

Per garantire la purezza del materiale e prevenire una nucleazione non uniforme, tutte le operazioni devono avvenire sotto vuoto o sotto protezione di gas inerte. Le tecniche tradizionali di sollevamento del silicio a cristallo singolo prevedono l'avvio di un collo sottile all'inizio della crescita del cristallo, definito "metodo del collo", per prevenire le dislocazioni del cristallo. Tuttavia, i progressi nella tecnologia di semina, in particolare l'infusione di una quantità significativa di boro nel cristallo seme, hanno rafforzato notevolmente la sua resistenza, evitando la necessità di un collo di 3 mm di diametro. Questo approccio innovativo sostituisce il metodo di necking vecchio di tre decenni, non solo facilitando la produzione di silicio a cristallo singolo di grandi dimensioni, ma anche accorciando i tempi di crescita del cristallo e migliorando i rendimenti, aprendo così la possibilità di produrre circuiti integrati su scala ultra-grande a costi contenuti.

Nella crescita dei wafer, il polisilicio viene introdotto in un crogiolo di quarzo all'interno di un forno, seguito da un lavaggio sotto vuoto o con gas inerte per creare uno stato fuso. Una volta che il silicio fuso si stabilizza, i cristalli singoli possono essere estratti utilizzando la direzione interna del cristallo seme predeterminata come guida sulla superficie liquida. Grazie al controllo preciso dell'altezza della superficie liquida del crogiolo, della temperatura dell'interfaccia solido-liquido e della velocità di rotazione del cristallo seme, il silicio si trasforma da liquido a solido, garantendo una direzione cristallina interna uniforme per la crescita di cristalli singoli di grande diametro. I processi di regolazione automatica computerizzati e le velocità di sollevamento garantiscono una crescita isotropa del silicio monocristallino.

Tabella 2 Wafer SOI vs. wafer di silicio

|

Wafer di silicio |

Wafer SOI |

||

|

Struttura |

Senza strato isolante |

Strato isolante |

|

|

Prestazioni |

Soppressione della diafonia |

No |

Sì |

|

Velocità e potenza |

Inferiore e superiore |

Più alto e più basso |

|

|

Resistenza alle radiazioni |

Più bassa |

Più alta |

|

|

Applicazioni |

Circuiti integrati |

Applicazioni ad alte prestazioni |

|

|

Celle solari |

Applicazioni a bassa potenza |

||

|

Dispositivi biomedici |

Ambienti ad alta radiazione |

||

|

Preparazione e costi |

SIMOX/BESOI/Smart-cut |

Metodo Czochralski |

|

|

Intricato |

Conveniente |

||

|

Costo elevato |

Basso costo |

||

4 Conclusioni

Esistono differenze significative tra i wafer SOI e i wafer di silicio in termini di struttura del materiale, caratteristiche delle prestazioni, aree di applicazione, ecc. La struttura SOI migliora le prestazioni e l'affidabilità dei dispositivi grazie alla struttura stratificata strato di silicio-strato isolante-substrato di silicio, ma con un costo di produzione più elevato. Al contrario, la produzione tradizionale di wafer di silicio è meno costosa e adatta a un'ampia gamma di circuiti integrati. Pertanto, nella scelta della struttura del materiale, i vantaggi e gli svantaggi di SOI e wafer di silicio devono essere valutati in modo esaustivo in base ai requisiti applicativi specifici e alle considerazioni sui costi per ottenere le migliori prestazioni e i migliori vantaggi economici.

Lettura correlata:

Riferimenti:

[1]Jin W ,Wei C ,Wanghua Z , et al. Ottimizzazione e confronto completo di sfasatori termo-ottici con guida d'onda ripiegata su piattaforme SiN e SOI[J]. Optics Communications, 2024, 555.

[2]Xin F ,Jiaqi N ,Shanglin Y , et al. Filtri ottici notch con lunghezza d'onda centrale sintonizzabile e intervallo spettrale libero riconfigurabile su piattaforma SOI[J]. Optics Communications, 2024,554.

[3]N. V ,A. M ,I. K , et al. Un nuovo array a barre incrociate di memorie resistive al nitruro di silicio su SOI consente la logica razionata dei memristori[J]. Elettronica dello Stato Solido, 2024,211.

Bar

Bar

Perline e sfere

Perline e sfere

Bulloni e dadi

Bulloni e dadi

Crogioli

Crogioli

Dischi

Dischi

Fibre e tessuti

Fibre e tessuti

Film

Film

Fiocco

Fiocco

Schiume

Schiume

Lamina

Lamina

Granuli

Granuli

Nidi d'ape

Nidi d'ape

Inchiostro

Inchiostro

Laminato

Laminato

Grumi

Grumi

Maglie

Maglie

Film metallizzato

Film metallizzato

Piatto

Piatto

Polveri

Polveri

Asta

Asta

Lenzuola

Lenzuola

Cristalli singoli

Cristalli singoli

Bersaglio di sputtering

Bersaglio di sputtering

Tubi

Tubi

Lavatrice

Lavatrice

Fili

Fili

Convertitori e calcolatori

Convertitori e calcolatori

Chin Trento

Chin Trento