L'impatto della qualità dei wafer di silicio sulle prestazioni e sull'affidabilità dei semiconduttori

1 Introduzione

Il mercato dei semiconduttori continua a crescere grazie alla ripresa economica. Le applicazioni emergenti, come il 5G e i veicoli a nuova energia, portano un nuovo ciclo di crescita all'industria globale dei semiconduttori. I dati della World Semiconductor Trade Statistics Organization (WSTS) mostrano che nel 2022 le dimensioni del mercato globale dei semiconduttori cresceranno del 3,3% rispetto all'anno precedente, raggiungendo il livello record di 574 miliardi di dollari.

In quanto materiale di base dei chip per semiconduttori, anche l'industria dei wafer di silicio entrerà in uno sviluppo ad alta velocità. Grazie alla ripresa della domanda di elettronica di consumo e all'aumento della domanda di focolai di intelligenza artificiale, il settore dei wafer da 12 pollici ha registrato una graduale ripresa nella seconda metà del 2023. Grazie all'accelerazione dello sviluppo delle imprese leader e alla graduale ripresa della domanda finale, il segmento realizzerà una crescita a due cifre nel 2024.

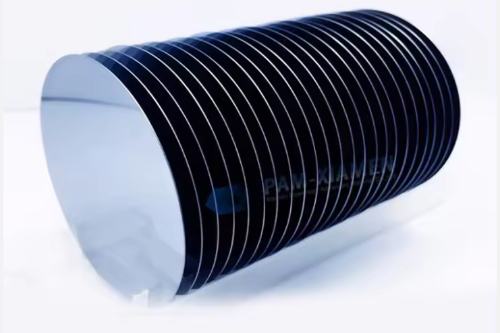

Essendo un materiale di base fondamentale nella produzione di semiconduttori, la qualità del cristallo dei wafer di silicio (Fig. 1) influisce direttamente sulle proprietà del dispositivo semiconduttore finito. L'effetto della qualità del reticolo e dei difetti dei bordi dei grani sulla mobilità degli elettroni dei wafer di silicio influisce direttamente sulla velocità e sul consumo di energia del dispositivo e può aumentare la corrente di dispersione del dispositivo. La planarità e il grado di contaminazione sulla superficie di un wafer di silicio possono avere un impatto significativo su fasi chiave come la litografia, la deposizione di film sottili e l'incisione. Le impurità e il drogaggio nei wafer di silicio possono portare a un maggiore intrappolamento degli elettroni, a una riduzione dei tempi di vita dei portatori e a una deriva dei parametri del dispositivo. Inoltre, durante la preparazione dei wafer di silicio e la successiva lavorazione possono essere introdotte sollecitazioni di temperatura e pressione che influiscono sulla stabilità meccanica e sulle proprietà elettriche dei cristalli.

2 Fattori chiave che determinano la qualità dei wafer di silicio

2.1 Struttura cristallina: Purezza del silicio a cristallo singolo, difetti del cristallo

I fattori chiave che determinano la qualità dei wafer di silicio in termini di struttura cristallina sono spesso indicati come purezza del cristallo e difetti del cristallo.

1. Purezza del cristallo: La purezza del silicio monocristallino è fondamentale per le sue proprietà elettriche. Il tipico silicio industriale (99,0-99,9%) non ha proprietà semiconduttrici, ma quando viene purificato a una purezza molto elevata (99,999999999%), mostra eccellenti proprietà semiconduttrici. Il silicio monocristallino di alta qualità raggiunge solitamente il 99,999999999% (9 su 9) o più a livello elettronico.

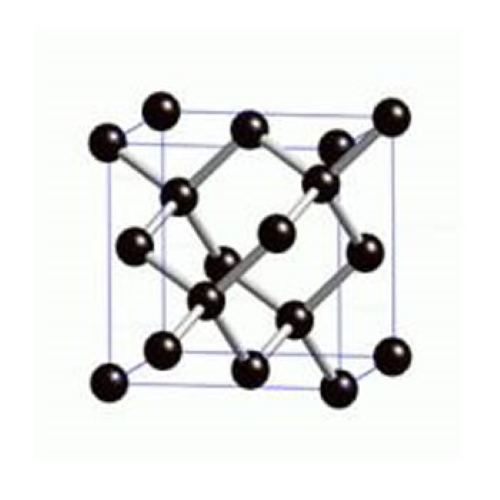

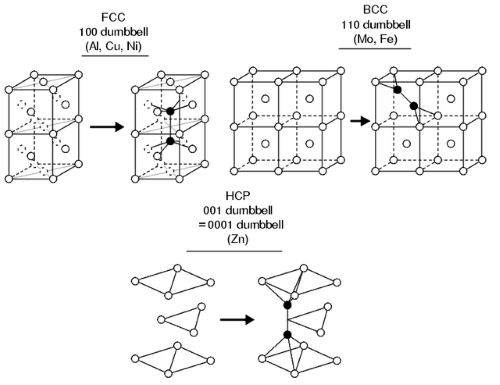

2. Difetti cristallografici: La matrice spaziale cristallina reale e la matrice spaziale ideale sono diverse, poiché non possono essere realizzate secondo la disposizione periodica regolare ideale (Fig. 2). Al contrario, nella disposizione ci sono irregolarità e aberrazioni, deviazioni dalla disposizione spaziale ideale. Le strutture o le regioni che si discostano dalla matrice di punti sono comunemente note come difetti del cristallo.

Tra questi, la dislocazione è un difetto del cristallo molto importante. La dislocazione di un cristallo è una linea molto lunga attorno alla quale gli atomi di un certo intervallo sono regolarmente disallineati, abbandonando la posizione di equilibrio originale, per cui viene chiamata dislocazione.

2.2 Qualità della superficie: Planarità, rugosità, contaminazione da particelle

1. Contaminazione superficiale: Questo difetto si riferisce a sostanze estranee come polvere, particelle e sostanze inquinanti attaccate alla superficie del wafer, che provengono dai detriti generati nei processi di taglio, lucidatura, pulizia, incisione, ecc. o dalla polvere presente nell'aria o dai residui di reagenti chimici. Queste ridondanze influenzano la planarità e la pulizia del wafer, nonché la qualità dei successivi processi di litografia, drogaggio e altro, che possono portare a difetti nella struttura del circuito integrato o a cambiamenti nelle caratteristiche elettriche del chip.

2. Danno meccanico: Questo difetto si riferisce alla superficie del wafer o al bordo del wafer con graffi, scheggiature, sbucciature e altri fenomeni, nel taglio del wafer, nella lucidatura, nella manipolazione e in altri processi generati dall'impatto o dall'attrito, oppure la qualità della lama o i parametri dell'inappropriato possono portare a una riduzione della planarità della superficie. Questi danni meccanici compromettono l'integrità e la stabilità del wafer e possono portare alla rottura o al distacco del chip.

2.3 Precisione dimensionale: Diametro, spessore e deformazione del wafer

Le dimensioni e lo spessore dei wafer non vengono scelti arbitrariamente, ma si basano sui requisiti di processo e sulle proprietà fisiche. Quando le dimensioni del wafer diventano più grandi, lo spessore del wafer viene aumentato di conseguenza per mantenerne la resistenza meccanica e la deformazione, evitando al contempo danni dovuti a sollecitazioni o piegature durante la lavorazione. Nel processo di produzione, i wafer sono sottoposti a vari trattamenti fisici e chimici, tra cui incisione, impiantazione di ioni, ossidazione, diffusione, ecc. Questi processi possono sottoporre il wafer a sollecitazioni meccaniche e, se il wafer è troppo sottile, può fratturarsi o rompersi. I wafer devono essere maneggiati e posizionati durante la lavorazione. Se il wafer è troppo sottile, può piegarsi, compromettendo la precisione della lavorazione.

3 Come i fattori di qualità dei wafer di silicio influenzano le prestazioni dei dispositivi a semiconduttore

3.1 Struttura del cristallo, difetti del reticolo

Le dislocazioni più comuni nei difetti reticolari hanno un impatto significativo sulle proprietà elettriche dei cristalli singoli di silicio. Ad esempio, le dislocazioni influenzano la resistività e la concentrazione dei portatori, accorciano la vita dei portatori minoritari e riducono la mobilità degli elettroni.

1. Effetto resistività: Le dislocazioni introducono campi di sollecitazione localizzati e non uniformi all'interno del cristallo, con conseguente aumento della dispersione di elettroni e buche. Questa dispersione porta al blocco della migrazione dei portatori, aumentando la resistività del materiale.

2. Effetti di concentrazione dei portatori: Le dislocazioni possono introdurre ulteriori atomi di impurità o modificare la disposizione degli atomi nel reticolo, cambiando così la concentrazione di portatori nel materiale semiconduttore. Ad esempio, un campo di stress localizzato in prossimità di una dislocazione può causare lo spostamento o la deformazione della posizione degli atomi, che a sua volta influisce sulla generazione e sulla soppressione dei portatori.

3. Riduzione della vita dei portatori minoritari: Le dislocazioni aumentano la complessità dei portatori nel materiale. Nei semiconduttori, la complessazione dei portatori porta a una riduzione dei tempi di vita dei portatori minoritari (ad esempio, elettroni o buchi entro la lunghezza di diffusione dei portatori minoritari). Il campo di stress localizzato e la non uniformità introdotta dalle dislocazioni possono aumentare l'interazione dei portatori e promuovere il processo di compounding.

4. Riduzione della mobilità degli elettroni: Le dislocazioni causano distorsioni e non uniformità nel reticolo cristallino, che possono ostacolare il movimento dei portatori all'interno del cristallo. In particolare, gli elettroni sono dispersi nel reticolo da difetti come le dislocazioni e i confini dei grani, il che riduce la mobilità degli elettroni.

3.2 Planarità della superficie

La planarità della superficie di un wafer di silicio ha un effetto a cascata sui dispositivi a semiconduttore. Non solo influisce direttamente sulla qualità della superficie di contatto con altri materiali o dispositivi, come elettrodi metallici e materiali di imballaggio. La qualità della superficie di contatto influisce direttamente sul valore della resistenza di contatto e una superficie di contatto non uniforme, sotto l'influenza di forze esterne che producono varie modifiche dei dati, avrà anche un impatto sulle prestazioni e sull'affidabilità del dispositivo.

Inoltre, la planarità della superficie del wafer di silicio, la contaminazione e altre condizioni della superficie influiscono sull'uso della fotolitografia e della tecnologia di incisione per definire la struttura. La tecnologia di incisione e la fotolitografia sono spesso utilizzate nel processo di produzione dei dispositivi a semiconduttore per incidere la struttura e il modello del dispositivo; le condizioni della superficie del wafer di silicio influenzano direttamente la precisione della fotolitografia e dell'incisione, la qualità e l'uniformità della grafica e la forma e le dimensioni del dispositivo prodotto hanno un ruolo decisivo.

I wafer di silicio sono un importante materiale di substrato per la deposizione di film sottili; la loro planarità superficiale influisce direttamente sulla qualità del film depositato sulla superficie. Difetti e contaminazioni sulla superficie dei wafer di silicio possono portare a una deposizione non uniforme del film, a incongruenze nello spessore del film, a bolle, crepe e altri difetti, compromettendo così le prestazioni e la stabilità del dispositivo.

3.3 Confini dei grani e impurità

La resistività di un semiconduttore è molto sensibile alla quantità di impurità che contiene. Anche piccole impurità possono influenzare seriamente le proprietà elettriche del silicio, come la conduttività e la mobilità dei portatori. In particolare, alcune impurità come ferro, rame e magnesio hanno un forte impatto sulle proprietà elettriche. La presenza di impurità può portare alla dispersione degli elettroni e alla non uniformità locale nel cristallo, riducendo così le prestazioni e l'affidabilità del dispositivo. Le variazioni del contenuto di impurità possono causare cambiamenti significativi nella resistività dei materiali semiconduttori. Ad esempio, quando la concentrazione di impurità di fosforo nel silicio varia nell'intervallo 1021-1012 cm-3, la sua resistività passa da 10-4 Ω.cm a 104 Ω.cm. Non sono molti i materiali la cui resistività può variare in un intervallo così ampio, il che dimostra che il contenuto di impurità dei semiconduttori è uno dei fattori principali nel determinare la loro resistività.

3.4 Dimensioni, spessore e deformazione del wafer

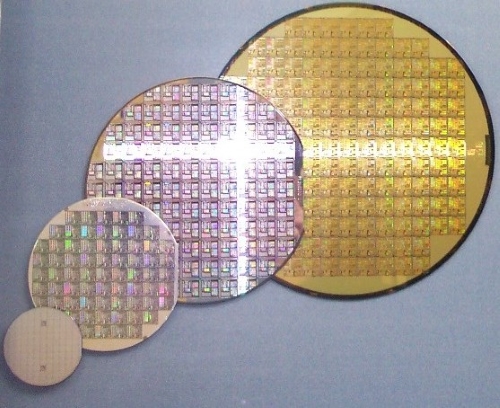

Nel processo di produzione, le dimensioni del wafer di silicio sono indubbiamente più favorevoli per il produttore. I wafer di silicio di grandi dimensioni e diametro possono produrre più dispositivi chip, l'efficienza di produzione delle apparecchiature può essere efficacemente migliorata; allo stesso tempo, il bordo del materiale sprecato sarà ridotto per ridurre i costi aggiuntivi, oltre a migliorare il tasso di riutilizzo delle apparecchiature.

Ma la dimensione del wafer di silicio non è una decisione arbitraria, dipende dalla capacità di lavorazione dell'apparecchiatura di produzione, perché il materiale stesso svolge il ruolo di stress, quando le dimensioni del wafer aumentano, il suo spessore dovrà essere aumentato di conseguenza, per mantenere la stabilità strutturale del materiale, altrimenti le dimensioni del wafer di spessore sottile e di grandi dimensioni saranno deformate da un corrispondente aumento dello spessore del materiale del wafer, che apparirà anche perdita di fratture e altri fenomeni.

4 Come la qualità dei wafer di silicio influisce sull'affidabilità dei semiconduttori

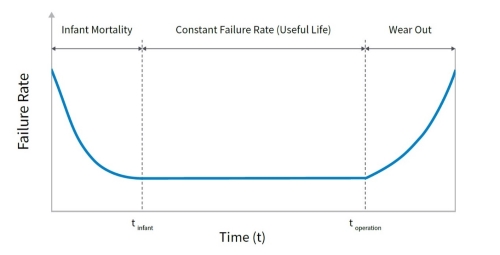

4.1 Effetto della densità dei difetti sulla durata del dispositivo

La vita di un dispositivo a semiconduttore è determinata principalmente dalla sua vita fisica e dalla sua vita di manutenzione. La vita fisica si riferisce al momento in cui un dispositivo a semiconduttore si guasta a causa dell'invecchiamento del materiale o dell'usura in condizioni operative normali. I difetti nei wafer di silicio possono accelerare il processo di invecchiamento del materiale, causando il guasto del dispositivo in un periodo più breve. Allo stesso tempo, i difetti possono anche causare perdite di corrente, riduzione della stabilità termica e altri problemi, compromettendo ulteriormente la durata del dispositivo.

La vita di riparazione è il tempo in cui un dispositivo a semiconduttore può essere riparato e continuare a funzionare normalmente dopo un guasto. Tuttavia, se la densità di difetti dei wafer di silicio è troppo elevata, può essere difficile ripristinare le prestazioni originali del dispositivo durante il processo di riparazione o rendere il costo della riparazione troppo elevato, riducendo così la durata della riparazione.

I difetti nei wafer di silicio influiscono anche sull'affidabilità dei dispositivi a semiconduttore. I difetti nella struttura cristallina causano un basso costo delle particelle rispetto alla posizione ideale della struttura cristallina, con conseguenti incollaggi in posizioni diverse e cambiamenti nella struttura cristallina, che si manifestano come sollecitazioni non uniformi, che possono portare all'instabilità o al guasto improvviso del dispositivo durante il funzionamento, compromettendo così la stabilità dell'intero sistema elettronico.

4.2 Relazione tra la qualità del wafer e la corrente di dispersione e la tensione di breakdown

La corrente di dispersione è la corrente che non dovrebbe fluire in un dispositivo a semiconduttore in condizioni di tensione operativa normale. In presenza di difetti in un wafer di silicio, come impurità, distorsioni reticolari, microfratture, ecc. questi difetti, così come le impurità, in particolare le particelle di impurità con proprietà conduttive, possono formare canali conduttivi che fanno fluire la corrente dove non dovrebbe, generando così una corrente di dispersione. La presenza di corrente di dispersione non solo aumenta il consumo di energia del dispositivo, ma può anche provocare l'aumento della temperatura del dispositivo, compromettendo ulteriormente le prestazioni e la durata.

La tensione di breakdown è la tensione massima che un dispositivo a semiconduttore può sopportare in condizioni operative normali. Al di là di questa tensione, il dispositivo può subire un guasto, ovvero un improvviso aumento della corrente, con conseguente danneggiamento del dispositivo. I difetti nei wafer di silicio possono ridurre la tensione di breakdown di un dispositivo perché in corrispondenza dei difetti si può verificare una concentrazione di campi elettrici o una fragilità strutturale che consente al dispositivo di rompersi a tensioni inferiori. Pertanto, la qualità del wafer di silicio ha un effetto significativo sulla tensione di breakdown.

5 Fabbricazione e controllo di qualità dei wafer di silicio

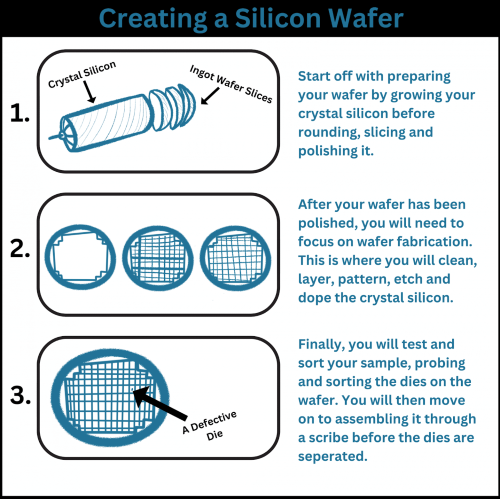

5.1 Tecnologia di crescita dei cristalli per i wafer di silicio

Il metodo Lift-off è oggi comunemente utilizzato per la crescita dei cristalli di silicio. Il crogiolo viene riempito di silicio e riscaldato in modo da mantenere la temperatura nel crogiolo a 1685°C. Questa temperatura è di circa 100°C superiore a quella di fusione. Questa temperatura è di circa 100°C superiore al punto di fusione del silicio da solo, quindi il silicio da solo nel crogiolo è in uno stato fuso. Nella parte superiore del crogiolo è presente un'asta di sollevamento e un dispositivo meccanico per far sollevare e ruotare liberamente l'asta di sollevamento. Un piccolo pezzo di silicio monocristallino viene immerso nel crogiolo fissandolo nella parte superiore della leva. Questo singolo cristallo di silicio funziona da "seme" e attira gli atomi di silicio circostanti a disporsi intorno ad esso per formare un cristallo. Il cristallo cresce mentre viene lentamente tirato e ruotato, e le parti che vengono estratte appartengono tutte allo stesso cristallo singolo. Il grande cristallo singolo ha un diametro di 200 millimetri, più spesso di un braccio. Un cristallo di questo tipo non ha interfacce, non ha difetti e si può dire che sia il cristallo singolo più perfetto che l'uomo possa realizzare. Per garantire la purezza del materiale ed evitare una nucleazione non uniforme, tutte le operazioni devono essere eseguite sotto vuoto o sotto protezione di gas inerte. Per evitare che si verifichino dislocazioni nel cristallo, il metodo tradizionale di sollevamento del silicio monocristallino consiste nel creare un collo sottile all'inizio della crescita della cristallizzazione, chiamato "metodo necking". A causa della forza del collo, è difficile sollevare silicio monocristallino di peso superiore a 100 chilogrammi. Gli scienziati hanno aggiunto una quantità considerevole di boro al cristallo seme, migliorando notevolmente la resistenza del cristallo seme, impedendo la dislocazione del cristallo, e quindi non è più necessario produrre un collo di 3 mm di diametro. Questo nuovo metodo, che sostituirà l'uso di 30 anni di metodo di necking, non solo è in grado di produrre silicio a cristallo singolo di grandi dimensioni, ma è anche in grado di abbreviare il tempo di crescita del cristallo e migliorare la resa, per la produzione a basso costo di circuiti integrati su scala ultra-grande necessari per fornire la possibilità di silicio a cristallo singolo di grandi dimensioni.

La crescita dei wafer richiede l'inserimento del polisilicio nel crogiolo di quarzo della fornace, nel vuoto o nel passaggio di gas inerte dopo la fusione. Dopo che il silicio fuso si è stabilizzato, i cristalli singoli possono essere estratti e un pezzo di cristallo seme che ha già determinato la direzione interna del cristallo viene utilizzato come guida sulla superficie liquida. Controllando l'altezza della superficie liquida del crogiolo, la temperatura dell'interfaccia solido-liquido e la velocità di rotazione del cristallo seme, il silicio si trasforma nuovamente da liquido a solido con una direzione cristallina interna uniforme per la crescita di cristalli singoli di grande diametro. Il processo di regolazione automatica e la velocità di sollevamento sono controllati da computer, il che garantisce la crescita isotropa del silicio monocristallino.

5.2 Tecnologia di trattamento superficiale dei wafer di silicio

Dopo il taglio, i wafer devono essere sottoposti a un trattamento superficiale per garantire la planarità della superficie del wafer e l'assenza di contaminazione da impurità. I metodi di trattamento più utilizzati sono la fotolitografia, l'incisione, ecc. Esistono anche alcune tecniche di pulizia, come la pulizia al plasma, che possono non solo pulire la superficie del wafer, ma anche migliorare l'attività superficiale, migliorare la capacità di adesione della superficie del materiale, migliorare la capacità di saldatura, l'idrofilia e così via.

Esistono inoltre alcuni metodi di trattamento innovativi, come il posizionamento del wafer in una camera di reazione con un gas di reazione; la reazione del gas di reazione con gli ossidi sulla superficie del wafer per formare un prodotto di reazione; la ricottura del wafer almeno due volte per decomporre e rimuovere il prodotto di reazione. Il metodo di trattamento superficiale consente di decomporre più volte i prodotti di reazione generati nel processo di trattamento superficiale mediante ricottura del wafer e ogni trattamento di ricottura scompone i prodotti di reazione in modo che lo spessore dei prodotti di reazione continui a diminuire, e allo stesso tempo riduce la difficoltà di decomposizione dei prodotti di reazione a causa dello spessore eccessivo dei prodotti di reazione e quindi facilita la decomposizione dei prodotti di reazione sulla superficie del wafer, riduce il numero di volte in cui il wafer viene ricotto durante il processo di trattamento superficiale e riduce il numero di volte in cui il metodo di trattamento superficiale viene ricotto. In questo modo si riduce la quantità di residui di prodotti di reazione sulla superficie del wafer durante il processo di trattamento superficiale.

5.3 Tecniche di ispezione per la qualità dei wafer di silicio

A causa della presenza di difetti nei wafer, durante i test di integrità funzionale di tutti i chip su un wafer possono verificarsi guasti ai chip. I tecnici dei chip contrassegnano i risultati dei test con colori diversi per distinguere la posizione dei chip. Sotto l'influenza di diversi processi operativi, sul wafer si generano di conseguenza modelli spaziali specifici. Hansen et al. nel 1997 hanno sottolineato che i chip difettosi di solito hanno fenomeni di aggregazione o presentano alcuni schemi sistematici, e questi schemi difettosi di solito contengono informazioni necessarie sulle condizioni di processo. La mappa del wafer non solo riflette l'integrità del chip, ma descrive anche accuratamente le informazioni sulla posizione spaziale corrispondenti ai dati sui difetti. La mappa del wafer può mostrare la dipendenza spaziale sull'intero wafer e i tecnici dei chip possono spesso risalire alla causa dei difetti e risolvere i problemi in base al tipo di difetto. Per i modelli di wafer con aree ampie, dimensioni ridotte, basse densità e bassa integrazione, i percorsi litografici possono essere osservati con un microscopio elettronico e il rilevamento delle tracce può essere eseguito direttamente. Per il rilevamento si può utilizzare anche un sistema di elaborazione del segnale dell'immagine, in cui il segnale dell'immagine viene decomposto in diverse sottobande di frequenza mediante filtri, quindi la media, la deviazione standard e altre statistiche come i coefficienti wavelet vengono rilevati e calcolati per individuare le anomalie.

6 Conclusioni

In quanto materiale fondamentale per la produzione di semiconduttori, la qualità del cristallo dei wafer di silicio influisce direttamente sulle proprietà dei dispositivi semiconduttori finiti. I progressi tecnologici nei processi di produzione e di analisi hanno portato a un graduale miglioramento della purezza e della precisione dei wafer di silicio, che in futuro saranno utilizzati in una gamma più ampia di applicazioni e di materiali più precisi. Per una migliore esperienza applicativa, Stanford Advanced Materials non solo fornisce prodotti di alta qualità per wafer di silicio, ma offre anche servizi completi, tra cui la consulenza e l'elaborazione post-vendita.

Lettura correlata:

Wafer di arseniuro di gallio VS. Wafer di silicio

Crescita e adesione del grafene ai wafer di silicio

Riferimenti:

[1]Masataka H ,Daiki T ,Oga N , et al. Studio sperimentale sull'effetto della concentrazione di impurità sulle proprietà di trasporto fononico ed elettronico del silicio a cristallo singolo[J]. Results in Physics,2023,47.

[2]Martin M ,P. P M ,Yi S B , et al. Effetto dello scattering dei confini dei grani sulla mobilità dei portatori e sulle proprietà termoelettriche di film sottili di ioduro di rame incorporato con tellurio[J]. Superfici e interfacce, 2023, 41.

Bar

Bar

Perline e sfere

Perline e sfere

Bulloni e dadi

Bulloni e dadi

Crogioli

Crogioli

Dischi

Dischi

Fibre e tessuti

Fibre e tessuti

Film

Film

Fiocco

Fiocco

Schiume

Schiume

Lamina

Lamina

Granuli

Granuli

Nidi d'ape

Nidi d'ape

Inchiostro

Inchiostro

Laminato

Laminato

Grumi

Grumi

Maglie

Maglie

Film metallizzato

Film metallizzato

Piatto

Piatto

Polveri

Polveri

Asta

Asta

Lenzuola

Lenzuola

Cristalli singoli

Cristalli singoli

Bersaglio di sputtering

Bersaglio di sputtering

Tubi

Tubi

Lavatrice

Lavatrice

Fili

Fili

Convertitori e calcolatori

Convertitori e calcolatori

Chin Trento

Chin Trento